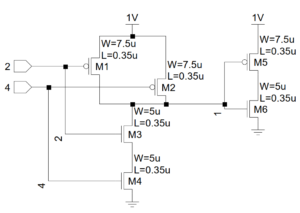

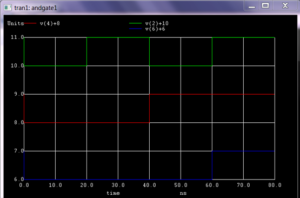

1] AND gate

*andgate1

.model n1 nmos level=10

.model p1 pmos level=10

vdd 3 0 1v

vss 0 0 0v

M1 3 2 1 3 p1 w=7.5u l=0.35u pd =13.5u ad=22.5p ps=13.5u as=22.5p

M2 3 4 1 3 p1 w=7.5u l=0.35u pd =13.5u ad=22.5p ps=13.5u as=22.5p

M3 1 2 5 0 n1 w=5u l=0.35u pd=9u ad=9p ps=9u as=9p

M4 5 4 0 0 n1 w=5u l=0.35u pd=9u ad=9p ps=9u as=9p

M5 3 1 6 3 p1 w=7.5u l=0.35u pd=13.5u ad=22.5p ps=13.5u as=22.5p

M6 6 1 0 0 n1 w=5u l=0.35u pd=9u ad=9p ps=9u as=9p

VA 2 0 pulse(1 0 0 0 0 20ns 40ns)

VB 4 0 pulse(1 0 0 0 0 40ns 80ns)

*cl 1 0 0.1f

.option acct

.tran 10ps 80ns

.print tran v(2) v(4) v(6)

.end

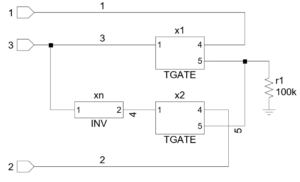

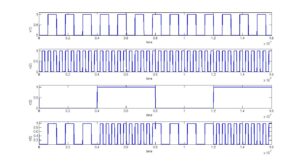

2]AMUX

*amux1

.subckt INV 1 2

.model n1 nmos level=10

.model p1 pmos level=10

vdd 3 0 1v

vss 0 0 0v

M1 3 1 2 3 p1 w=7.5u l=0.35u pd =13.5u ad=22.5p ps=13.5u as=22.5p

M2 2 1 0 0 n1 w=5u l=0.35u pd=9u ad=9p ps=9u as=9p

.ends

.subckt TGATE 4 1 5

.model n1 nmos level=10

.model p1 pmos level=10

vdd 3 0 1v

vss 0 0 0v

x1 1 2 INV

M1 5 1 4 3 p1 w=7.5u l=0.35u pd =13.5u ad=22.5p ps=13.5u as=22.5p

M2 4 2 5 0 n1 w=5u l=0.35u pd=9u ad=9p ps=9u as=9p

.ends

x1 1 3 5 TGATE

xn 3 4 INV

x2 2 4 5 TGATE

r1 5 0 100k

VA 1 0 pulse(1 0 0 0 0 6ns 12ns)

VB 2 0 pulse(1 0 0 0 0 2ns 4ns)

VC 3 0 pulse(1 0 0 0 0 40ns 80ns)

.option acct

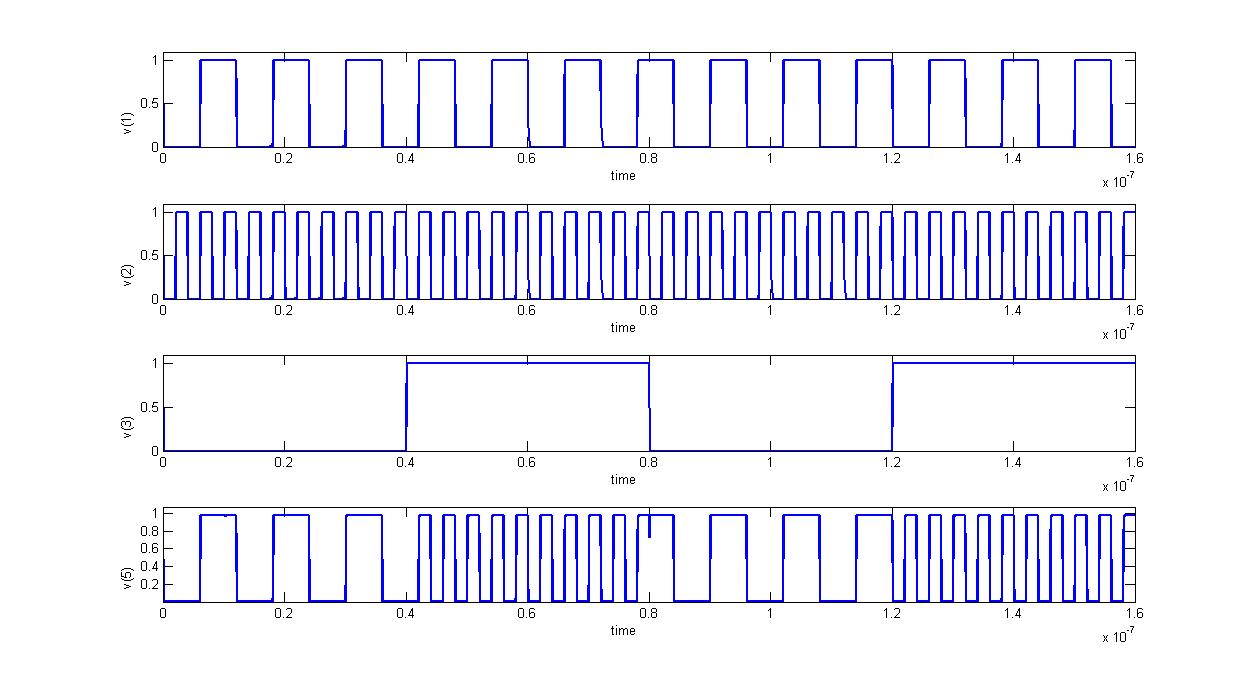

.tran 0.1ns 160ns

.print tran v(1) v(2) v(3) v(5)

.end

Thank you for the auspicious writeup. It in fact was a amusement account it. Look advanced to far added agreeable from you! By the way, how could we communicate?

Hi just wanted to give you a quick heads up and let you know a few of the pictures aren’t loading correctly. I’m not sure why but I think its a linking issue. I’ve tried it in two different internet browsers and both show the same results.

Can you be more specific about the content of your article? After reading it, I still have some doubts. Hope you can help me.

Thank you for your sharing. I am worried that I lack creative ideas. It is your article that makes me full of hope. Thank you. But, I have a question, can you help me?

Your point of view caught my eye and was very interesting. Thanks. I have a question for you.

I don’t think the title of your article matches the content lol. Just kidding, mainly because I had some doubts after reading the article.

Thanks for sharing. I read many of your blog posts, cool, your blog is very good.

Sharing is caring the say, and you’ve done a fantastic job in sharing your knowledge on your blog. It would be great if you check out my page, too, at QN7 about Car Purchase.

Your point of view caught my eye and was very interesting. Thanks. I have a question for you.

Can you be more specific about the content of your article? After reading it, I still have some doubts. Hope you can help me.

Your point of view caught my eye and was very interesting. Thanks. I have a question for you.

Thanks for sharing. I read many of your blog posts, cool, your blog is very good.

Your article helped me a lot, is there any more related content? Thanks!

Your article helped me a lot, is there any more related content? Thanks!

Your point of view caught my eye and was very interesting. Thanks. I have a question for you.

Can you be more specific about the content of your article? After reading it, I still have some doubts. Hope you can help me.

Can you be more specific about the content of your article? After reading it, I still have some doubts. Hope you can help me. https://www.binance.com/register?ref=P9L9FQKY

Serving Iraq with pride, BWER supplies high-performance weighbridges designed to improve transport logistics, reduce inaccuracies, and optimize industrial processes across all sectors.