The communication between the two modules, which is operating at different clock speed. To ensure the lossless data transfer, there are few methods thro which we can make it happens. One of the method which will ensure the data integrity is FIFO technique. Where a FIFO is place between these two modules, and each modules communicate to FIFO for the data store and transfer.

We are keeping the following notation

module A – writing module module B – reading module

fa – writing clock speed fb – reading clock speed

burst length – no of data items to be transferred

ideal cycles – there is ideal cycles in between reading and writing

There are certain practical cases based on speed like fa > fb , fb > fa etc.

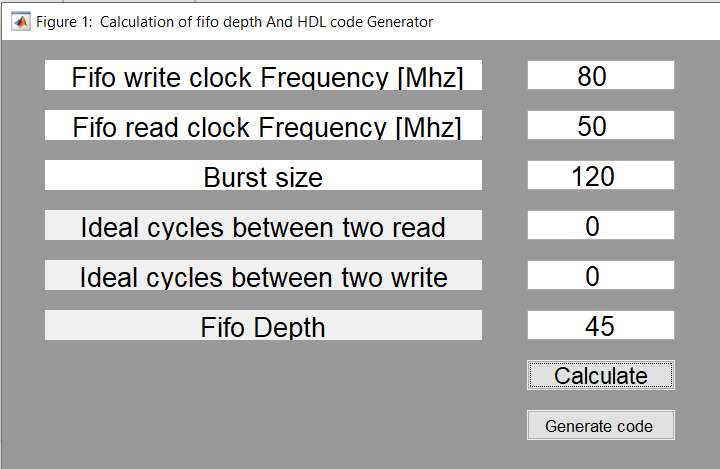

Ex1] if fa> fb with no idle cycles in both write and read.

Writing frequency fa = 80MHz

Reading Frequency fb = 50MHz

Burst Length = 120

There are no idle cycles in both reading and writing which means that,

all the items in the burst will be written and read in consecutive clock cycles.

Time required to write one data item = 1/80MHz = 12.5 nSec.

Time required to write all the data in the burst = 120 * 12.5 nSec. = 1500 nSec.

Time required to read one data item = 1/50MHz = 20 nSec.

So, for every 20 nSec, the module B is going to read one data in the burst.

So, in a period of 1500 nSec, 120 no. of data items can be written.

And the no. of data items can be read in a duration of 1500 nSec = 1500 nSec/20 nSec = 75

The remaining no. of bytes to be stored in the FIFO = 120 – 75 = 45.

So, the FIFO which has to be in this scenario must be capable of storing 45 data items.

Will cross validate from our calculator

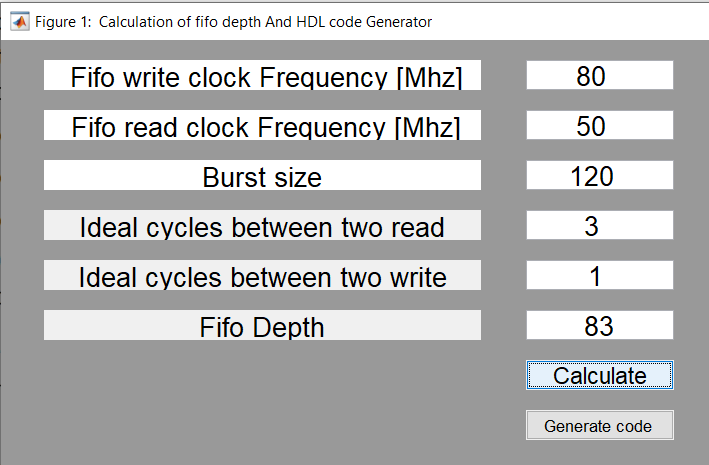

Ex.2] if fa> fb with idle cycles in both write and read.

Writing frequency = fa = 80MHz

Reading Frequency = fb= 50MHz

Burst Length = 120.

No. of idle cycles between two successive writes is = 1.

No. of idle cycles between two successive reads is = 3

The no. of idle cycles between two successive writes is 1 clock cycle. It means that, after

writing one data, module A is waiting for one clock cycle, to initiate the next write.

So, it can be understood that for every two clock cycles, one data is written.

The no. of idle cycles between two successive reads is 3 clock cycles. It means that, after

reading one data, module B is waiting for 3 clock cycles, to initiate the next read. So, it

can be understood that for every four clock cycles, one data is read.

Time required to write one data item = 2*1/80MHz = 25 nSec

Time required to write all the data in the burst = 120 * 25 nSec. = 3000 nSec.

Time required to read one data item = 4*1/50MHz = 80 nSec.

So, for every 80 nSec, the module B is going to read one data in the burst.

So, in a period of 3000 nSec, 120 no. of data items can be written.

The no. of data items can be read in a period of 3000 nSec = 3000 nSec/80 nSec = 37.5 ~ 37

The remaining no. of bytes to be stored in the FIFO = 120 – 37 = 83.

So, the FIFO which has to be in this scenario must be capable of storing 83 data items

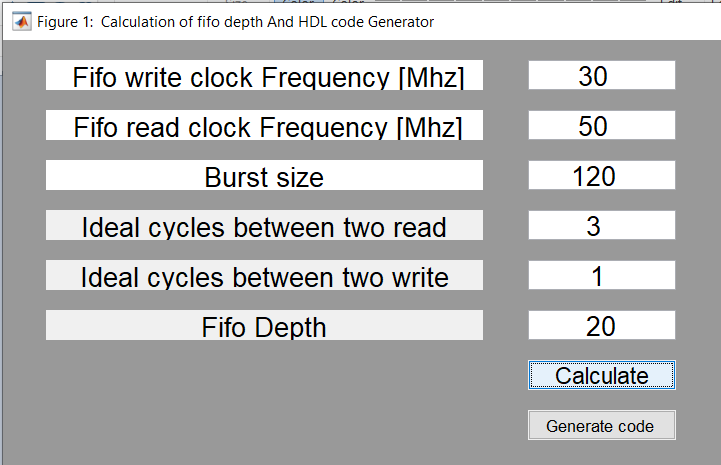

Ex3] if fa< fb with idle cycles in both write and read (duty cycles of wr_enb and rd_enb can also be given in these type of questions).Writing frequency = fa = 30MHz.Reading Frequency = fb = 50MHz. Burst Length = No. of data items to be transferred = 120. No. of idle cycles between two successive writes is = 1. No. of idle cycles between two successive reads is = 3.

The no. of idle cycles between two successive writes is 1 clock cycle. It means that, after

writing one data, module A is waiting for one clock cycle, to initiate the next write. So, it

can be understood that for every two clock cycles, one data is written.

The no. of idle cycles between two successive reads is 3 clock cycles. It means that, after

reading one data, module B is waiting for 3 clock cycles, to initiate the next read. So, it

can be understood that for every four clock cycles, one data is read.

Time required to write one data item = 2*1/30 = 66.667nSec.

Time required to write all the data in the burst = 120 * 66.667 nSec. = 8000 nSec.

Time required to read one data item = 4*1/50MHz = 80nSec

So, for every 80 nSec, the module B is going to read one data item in the burst.

So, in a period of 8000 nSec, 120 no. of data items can be written.

The no. of data items can be read in a period of 8000 nSec = 8000/80 = 100

The remaining no. of bytes to be stored in the FIFO = 120 – 100 = 20.

So, the FIFO which has to be in this scenario must be capable of storing 20 data items.

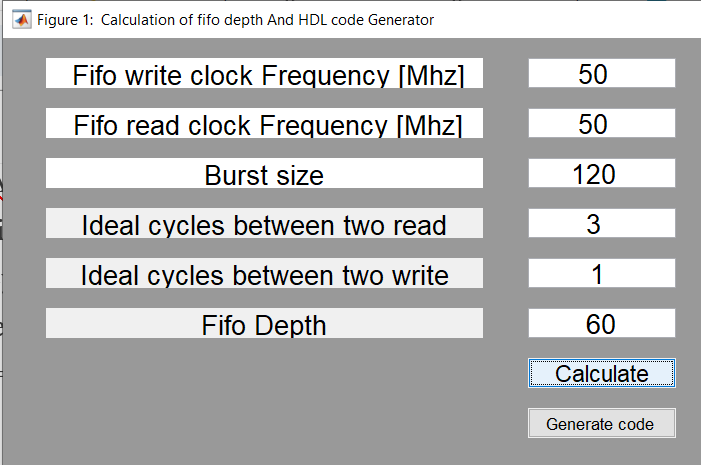

ex4] if fa = fb with idle cycles in both write and read (duty cycles of wr_enb and rd_enb can also be given in these type of questions).Writing frequency = fa = 50MHz.Reading Frequency = fb = 50MHz.Burst Length = No. of data items to be transferred = 120.No. of idle cycles between two successive writes is = 1.No. of idle cycles between two successive reads is = 3

The no. of idle cycles between two successive writes is 1 clock cycle. It means that, after

writing one data, module A is waiting for one clock cycle, to initiate the next write. So, it

can be understood that for every two clock cycles, one data is written.

The no. of idle cycles between two successive reads is 3 clock cycles. It means that, after

reading one data, module B is waiting for 3 clock cycles, to initiate the next read. So, it

can be understood that for every four clock cycles, one data is read.

Time required to write one data item = 2 ∗ 1/50Mhz = 40 nSec.

Time required to write all the data in the burst = 120 * 40 nSec. = 4800 nSec.

Time required to read one data item = 4 ∗ 1/50 = 80 nSec

So, for every 80 nSec, the module B is going to read one data item in the burst.

So, in a period of 4800 nSec, 120 no. of data items can be written.

The no. of data items can be read in a period of 4800 nSec = 4800/80 = 60

The remaining no. of bytes to be stored in the FIFO = 120 – 60 = 60.

So, the FIFO which has to be in this scenario must be capable of storing 60 data items

Please feel free to communicate for any farther help or support.

Thanks